## Spintronics: A New Paradigm for Electronics for the New Millennium

Stuart A. Wolf and Daryl Treger

*Abstract*—SPIN TRansport eletrONICS or SPINTRONICS, in which the spin degree of freedom of the electron will play an important role in addition to or in place of the charge degree of freedom in mainstream electronics will be important as we start the new millennium. The prospects for this new electronics in nonvolatile radiation hard magnetic memory for the Department of Defense (DoD) will be described.

Index Terms—Non-volatile magnetic memory, spin transport, spintronics.

## I. INTRODUCTION

**F** ORTY years ago, in a talk given to the American Physical Society, Richard Feynman challenged his audience to build computers with wires no wider than 100 atoms, a microscope that can image individual atoms, a machine that can manipulate atoms one by one and circuits that utilize quantized energy levels or the interaction of *quantized spins*. It is the very last, but certainly not least item in Feynman's list that will be the subject of this article.

Clearly, the progress in electronics over these last forty years has proven that scientists and engineers were up to Feynman's challenge. However, until very recently, the spin of the electron was ignored in mainstream electronics. Adding the spin degree of freedom to electronics will provide significantly more capability and performance to future electronic products and we have just seen the tip of the iceberg with the recent introduction of very high performance disk drives utilizing Giant Magneto-Resistive (GMR) read heads. Indeed, there are many ways that the spin of the electron can be utilized to add new capabilities and new functionality [1]. These range from near term products like nonvolatile, very high density, very high speed, very low power random access memories to the longer-term very esoteric realm of quantum computing [2], [3].

When GMR was discovered by Albert Fert's group in France in 1988, the first steps on the road to the utilization of the spin degree of freedom of the electron were taken [4]. It took about 10 years for the fruits of this discovery to ripen with the appearance of very high density disk storage, first introduced by IBM and quickly followed by many other manufacturers in the US and Japan. A GMR device consists of alternate layers of ferromagnetic and nonmagnetic metals whose resistance depends on the relative orientation of the magnetic layers. The basis for

Manuscript received February 15, 2000; revised May 15, 2000.

S. A. Wolf is with the Defense Sciences Office, DARPA, Arlington, VA 22203 USA and the Naval Research Laboratory, Code 6300.4, Washington DC 20375 USA.

D. Treger is with the Strategic Analysis Inc., Arlington, VA 22201 USA. Publisher Item Identifier S 0018-9464(00)08332-1.

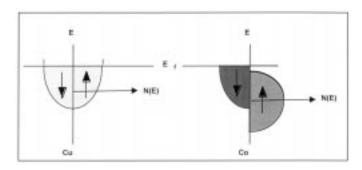

Fig. 1. Partial spin polarization in ferromagnetic metals.

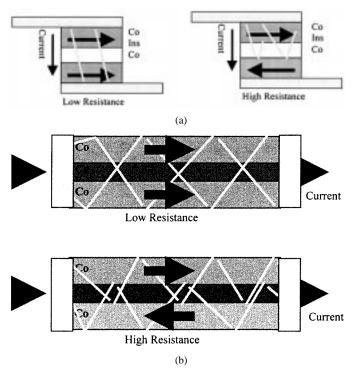

Fig. 2. Comparison of spintronic devices where current is (a) Perpendicular to the Plane (CPP) and (b) Current is In-Plane (CIP).

GMR and related devices is that in ferromagnetic metals the electrons at or very near the Fermi surface (which are the only ones that contribute to transport phenomenon) are partially spin polarized. This is illustrated in Fig. 1.

The larger the degree of spin polarization of these electrons the bigger the spin transport effects. If the ferromagnetic layers have their moments all aligned then the device has very low resistance, alternatively if alternate layers are anti-aligned, then the device has high resistance and as the alignment changes so does the resistance. This response is illustrated in Fig. 2.

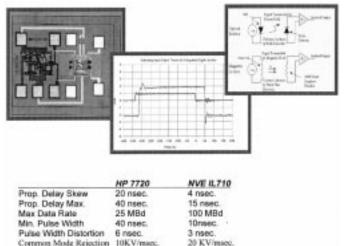

Fig. 3. NVE GMR Digital Isolator.

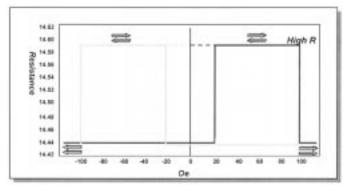

Fig. 4. Magnetic response of an ideal spin valve.

The current can either be perpendicular to the interfaces (CPP) as is shown in the top part of the Fig. 2 or can be parallel to the interfaces as shown in the bottom part of the figure (CIP). In both cases the change in resistance can be quite large and can be controlled by the relative orientation of the moments of the two magnetic layers. Although the various layers have to be very thin, modern deposition technology can control the deposition processes to the sub-Angstrom level.

Sensors can be made from these multilayers and Non-Volatile Electronics Inc. (NVE), a small high-tech company, has developed a range of sensors, switches and isolators based on these materials. The cost and power are extremely low, making these devices highly competitive. The performance of the isolators in particular, can be much better than their optical counterparts at lower cost. This is shown in Fig. 3.

The structures illustrated in Fig. 2 can be optimized to make a nonvolatile, high density memory cell. Fig. 4 shows an idealized hysteretic response that shows the memory possibilities of these structures.

Several scientists and engineers in the US including Gary Prinz from the Naval Research Laboratory, Jim Daughton from NVE, and Gerry Granley from Honeywell were convinced that memories built from these devices could ultimately compete with mainstream semiconductor memories in density, speed, and cost, with the important added bonus of nonvolatility and

Fig. 5. Honeywell 16 Kb GMR MRAM device.

Fig. 6. Honeywell 1 Mb MRAM device.

the potential for significant tolerance to extremely harsh environments. In 1995, the GMR Consortium Project was initiated at DARPA and one of us (S.A.W.) was the initiator as well as the Program Manager. This project had as its goal the exploration of the utility of GMR devices for various sensor and memory applications. This project culminated in the demonstration of a 16 Kbit nonvolatile, radiation hard, magnetic random access memory chip that was under a square inch in size and had an access time of under 100 nanoseconds. This memory was developed by Honeywell using their radiation hard CMOS underlayers that were developed under an ARMY program that was simultaneously developing a magnetic memory chip based on anisotropic magnetoresistance (AMR). The GMR memory was at least a factor of four faster based on the larger changes in resistance that GMR afforded [5]. A picture of this chip is shown in Fig. 5.

This original GMR Consortium soon became a regular and significantly larger DARPA project which one of us (S.A.W.) named Spintronics which is a shortened version of spin-transport-electronics. This program now had the charter to explore other devices beyond GMR and in particular spin dependent tunneling structures and unusual magnetic oxides. Spintronics now includes Motorola and IBM in addition to Honeywell, and many academic and laboratory participants.

TABLE I

COMPARISON OF MEMORY TECHNOLOGIES

|                         | CMOS                                              |                       |              | MRAM                  |

|-------------------------|---------------------------------------------------|-----------------------|--------------|-----------------------|

| Technology              | DRAM                                              | Flash                 | SRAM         | MRAM                  |

| Reference               | SIA 1997                                          | SIA 1997              | SIA 1997     |                       |

| No. of Devices          | 256GB                                             | 256GB                 | 180MB/cm 2   | >256GB                |

| Circuit Speed           | 150 MHz                                           | 150 MHz               | 913 MHz      | >500 MHz              |

| Feature Size            | 50 nm                                             | 50 nm                 | 35 nm        | <50 nm                |

| Access Time             | 10 ns                                             | 10 ns                 | 1.1 ns       | < 2 ns                |

| Write Time              | 10 ns                                             | 10 µs                 |              | < 10 ns               |

| Erase Time              | < 1 ns                                            | 10 µs                 |              | N/A                   |

| Retention Time          | 2-4 s                                             | 10 years              |              | Infinite              |

| Endurance Cycles        | Infinite                                          | 10 5                  | Infinite     | Infinite              |

| Operating Voltage (V)   | 0.5-0.6 V dd                                      | 5 V pp                | 0.6-0.5 V dd | < 1V                  |

| Voltage to Switch State | 0.2 V                                             | 5 V                   |              | < \$0mV               |

| Cell Size               | 2.5 F <sup>2</sup> /bit<br>0.0005 μm <sup>2</sup> | 2 F <sup>2</sup> /bit |              | 2 F <sup>2</sup> /bit |

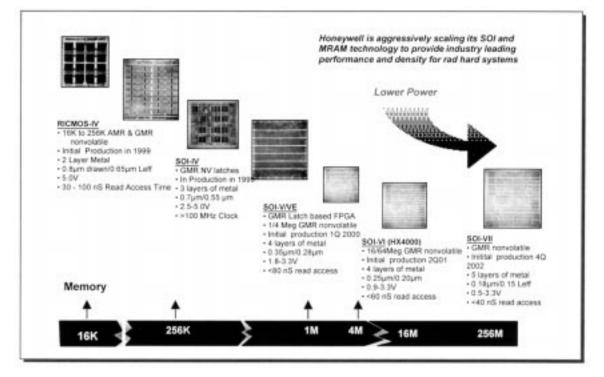

Fig. 7. Honeywell roadmap.

One of the reasons for the significant interest in this memory apart from the clear DoD applications, is the very favorable comparison of the potential performance of this memory to other nonvolatile memories like FLASH but also the favorable comparison to mainstream volatile memories like DRAM and SRAM. Table I shows a projection of the 2012 performance of some of the usual semiconductor memories based on the 1997 SIA roadmap compared with a projection based on what we expect from MRAM. This memory also has some additional features which are very important to the DoD.

The memory has unlimited read and write. This is better than ferroelectric-RAM (FeRAM) which still is limited in the number of times it can be cycled. The memory has a nondestructive read out (NDRO) so that the information will not be lost and the data storage has very high integrity. It is intrinsically radiation hard and is limited only by the radiation hardness of the silicon circuits which control it.

Motorola and IBM are developing memories based on the spin dependent tunneling device similar to a GMR cell, but with the nonmagnetic metal replaced by an insulating tunnel barrier. Their geometry is the CPP geometry and as illustrated in Fig. 2, with the magnetic layers being separated by a very thin insulating aluminum oxide barrier. The advantage of this Tunneling Magneto-Resistance (TMR) device is a very large effective magneto-resistance ratio (at least 40 per cent), but the penalty is the very thin insulator (10–15 Angstroms) requiring uniformity over many square inches [6].

The DARPA program is reaching a stage where successively more advanced prototypes are scheduled to be demonstrated in the next few years starting with a 1 Mbit memory chip. Honeywell is well on the way to demonstrating such a memory and Fig. 6 is a picture of the Honeywell 1 Mbit chip.

The memory shown in Fig. 6 is manufactured on commercial CMOS underlayers with the wiring and magnetics done in a back-end-of-the-line (BEOL) process. Future versions of this chip will be fully radiation hard and designed for severe environmental and radiation exposures. IBM and Motorola also have demonstrations planned for the near future and the roadmap for this technology is quite aggressive. Fig. 7 is a current version of the Honeywell roadmap as an example.

As indicated in the Table I, the prospects for this memory are excellent and there are just a few remaining hurdles. In particular, understanding and controlling the rotation of one of the magnetic layers rapidly, reproducibly and without disturbing neighboring bits remains a challenge, but rapid progress is being made in this area and it does not appear be a showstopper.

There is also excellent work in Japan and Europe that looks at both GMR and TMR devices and their potential, but as far as we know, the DARPA program is unique in trying to provide all of the infrastructure necessary to build fully functional memory prototypes that can be rapidly productized. We expect that this situation will change dramatically as soon as products begin to appear early next millennium.

The future for the current spintronics program is quite bright and the transition to both commercial and military products should occur within the next few years. However the possibility to demonstrate many more spintronic devices like spin-FET's, spin-LED's, spin-resonant tunneling devices, spin coherent devices and spin quantized devices are real and on the horizon [7]–[9]. We hope to soon report on spin-based technology which will further revolutionize the electronics industry.

## REFERENCES

- [1] G. Prinz, "Magnetoelectronics," Science 282, pp. 1660–1663, 1998.

- [2] D. P. DiVincenzo, "Quantum computation," Science 270, pp. 255–261, 1995.

- [3] D. Loss and D. P. DiVincenzo, "Quantum computation with quantum dots," *Phys Rev.*, vol. A-57, pp. 120–126, 1998.

- [4] M. Baibich et al., Phys. Rev. Lett., vol. 61, p. 2472, 1988.

- [5] M. Dax, Semiconduct. Int'l., vol. 20, no. 10, p. 84, 1997.

- [6] S. S. P. Parkin *et al.*, "Exchange-bias magnetic tunnel junctions and application to nonvolatile magnetic random access memory," *J. App. Phys.*, vol. 85, p. 5828, 1999.

- [7] Y. Ohno *et al.*, "Electrical spin injection in a ferromagnetic semiconductor heterostructure," in *Nature Volume 402*, December 1999, p. 16.

- [8] H. Ohno et al., "(Ga, Mn) As: a new diluted magnetic semiconductor based on GaAs," Appl. Phys. Lett, vol. 69, pp. 363–365, 1996.

- [9] D. Awschalom and J. M. Kikkawa, "Electron spin and optical coherence in semiconductors," *Phys. Today*, vol. 52, pp. 33–38, 1999.